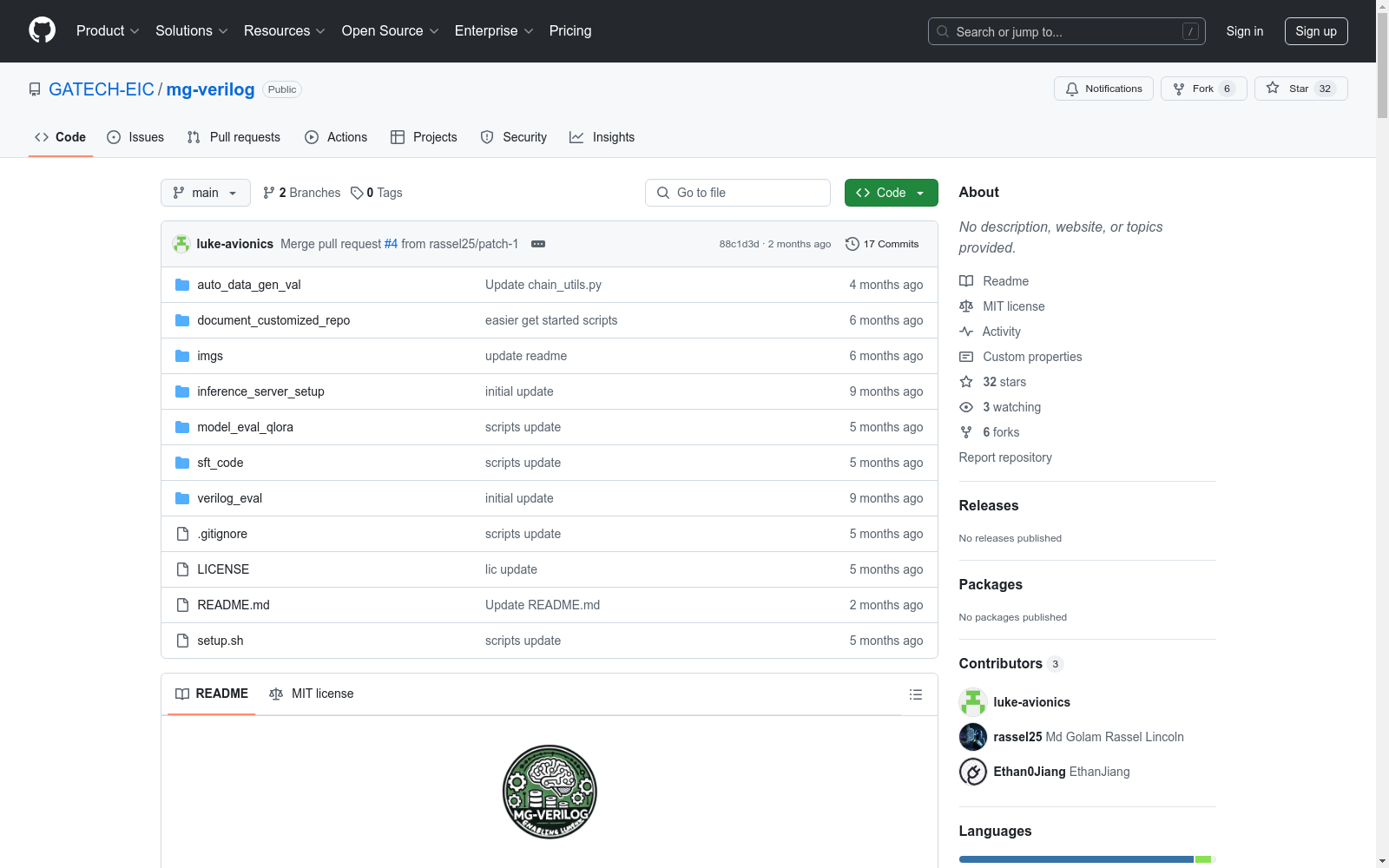

MG-Verilog

收藏MG-Verilog 数据集概述

数据集生成

原始数据集预处理

- 来源:Benchmarking Large Language Models for Automated Verilog RTL Code Generation

- 内容:包含超过10万条来自开源实现的代码样本。

- 预处理工具:PyVerilog 和 Icarus Verilog (iverilog)

- 步骤: bash $ cd auto_data_gen_val/preprocess_data/process_data $ python preprocess.py ./raw_dataset_output_path/ $ cd ../../

数据集划分

- 目的:为了更灵活的描述生成和组织元数据(如模块依赖),将数据集划分为不同的部分。

- 步骤: bash $ python utils.py --src_code_dir ./preprocess_data/process_data/raw_dataset_output_path/ --src_code_metadata_file ./preprocess_data/process_data/module_inst.json --output_dir ./partitioned_dataset_output_path/ --shared_lib_dir ./directory_to_store_common_modules/ --output_code_metadata_dir ./output_dir_for_code_metadata/ --output_code_metadata_file codes.json --module_to_task_id_map_file ./preprocess_data/process_data/module_name_to_task_id_mapping.json

PoT 数据集生成

- 主要模型:

LLAMA2-70B-Chat,备用模型openai-gpt3.5-turbo/4 - 步骤:

-

逐行注释生成: bash $ python line_by_line_comments_gen.py --total_parts 10 --output_dir ./documented_code --src_code_dir ./partitioned_dataset_output_path/ --code_metadata_dir ./output_dir_for_code_metadata/ --code_lib_path ./directory_to_store_common_modules/ --code_vec_store ../code_vec_store/test/ --discard_original_comment

-

块摘要生成: bash $ python gen_block_summaries.py 0 10 --code_metadata_dir ./output_dir_for_code_metadata/ --documented_code_dir ./documented_code --block_line_length 10 --model gpt-3.5-turbo-1106

-

全局摘要生成: bash $ python gen_global_summary.py 0 10 --documented_code_dir ./documented_code --model gpt-3.5-turbo-1106 --detailed $ python gen_global_summary.py 0 10 --documented_code_dir ./documented_code --model gpt-3.5-turbo-1106

-

数据集打包: bash $ python dataset_utils.py --doced_dataset_dir ./documented_code --total_part 10 --packaged_dir ./packaged_dataset --package_detailed_description --package_simple_description --package_llm2_block_summary_to_pure_code_one_shot_dataset --package_merged_dataset

-

基准准备

- 来源:HDLBits

- 步骤: bash $ python verilog_eval_to_part_data.py --eval_file ../verilog_eval/data/VerilogEval_Machine.jsonl --data_dir ./benchmark_code_files/ --meta_data_dir ./benchmark_metadata_files/ $ python line_by_line_comments_gen.py --total_parts 1 --output_dir ./benchmark_documented_code --src_code_dir ./benchmark_code_files/ --code_metadata_dir ./benchmark_metadata_files/ --code_lib_path ./benchmark_code_files/ --code_vec_store ../benchmark_code_vec_store/test/ --skip_supplement_summary --discard_original_comment $ python gen_block_summaries.py 0 1 --documented_code_dir ./benchmark_documented_code --block_line_length 10 --model gpt-3.5-turbo-1106 $ python gen_global_summaries.py 0 1 --documented_code_dir ./benchmark_documented_code --model gpt-3.5-turbo-1106 --detailed $ python gen_global_summaries.py 0 1 --documented_code_dir ./benchmark_documented_code --model gpt-3.5-turbo-1106 $ python dataset_utils.py --doced_dataset_dir ./benchmark_documented_code --total_part 1 --packaged_dir ./benchmark_packaged_dataset --package_hdlbits_global_summary_description_file --package_hdlbits_block_summary_description_file

数据集验证

- 工具:Icarus Verilog (iverilog) 和 GPT-4

- 步骤: bash $ python code_validate.py --dataset_dir ./packaged_dataset/detailed_description_dataset --output_dir ./packaged_dataset/detailed_description_dataset_val

监督微调

-

目的:使用 PoT 数据集进行模型微调和性能评估。

-

步骤: bash cd .. cd sft_code ./train.sh

-

评估: bash cd .. cd model_eval_qlora ./gen.sh

收集的数据集和微调模型检查点

- 数据集:drive_link

- 模型检查点:drive_link

- 1MG-Verilog: Multi-grained Dataset Towards Enhanced LLM-assisted Verilog Generation佐治亚理工学院 · 2024年